惠州市岚方实业有限公司

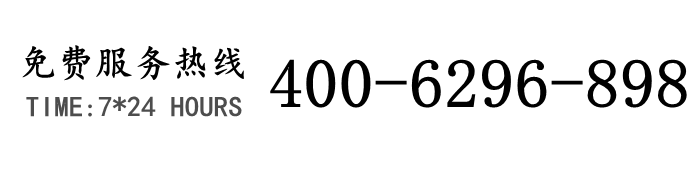

电话:400-6296-898

传真:0752-2042189

邮箱:sales@lanfsy.com

地址:惠州市博罗县罗阳镇西北路8号

邮编:516100

抖动与相噪有什么关系?

相位噪声和抖动是对同一种现象的两种不同的定量方式。抖动是一个时域概念,单位是pS或fS。相位噪声是频率域的概念,相位噪声是用偏移频率fm处1Hz带宽内的矩形的面积与整个功率谱曲线下包含的面积之比表示的,单位为-dBC/Hz。

OCXO的电压参考端的作用是什么?

通常时钟板上需要一个高精密的电压基准,解决的办法可以在时钟设计上增加一个高精密的电压基准芯片,但这样会带来时钟成本的上升。另外的解决办法可以从OCXO的电压参考端获得电压基准。由于OCXO通常是将电压基准放置在温度最恒定的地方,而且OCXO的恒温槽的控温精度通常为0.1℃,这样无形进一步减小了电压基准对温度变化的敏感程度。所以推荐采取OCXO电压参考端作为时钟的电压基准。

压控纹波是否会影响晶振的稳定性

如果晶振压控电压发生改变,晶振的频率必然也随之变化。当干扰信号过大时会带来晶振抖动或相噪恶化,甚至发生频率改变。通常在晶振内部压控端设计了频响大于2KHZ的低通滤波回路以减小压控端外来纹波的干扰。 如晶振工作环境存在较强外部干扰时,也可以在压控端外部增加低通滤波器。

晶振供电源系统设计应该注意哪些事项?

在晶振的电源输入端跨接一个10~100uF的钽电容或陶瓷电容,供电电压越低或供电PCB走线越细,电容的容值应相应增大以降低将纹波干扰。 除此之外,在晶振的电源输入端还应该跨接一个0.01uF的陶瓷去耦电容,推荐采取”同层相连”的方法,切不可通过过孔在电源层和地线层相连。 对于OCXO产品还应该注意供电系统的功率需大于OCXO的启动功率并有一定的余量。

时钟系统PCB排版应该注意哪些事项

从PCB布线上考虑,基本原则如下:

◎输入线和输出线避免相邻平行,以免产生反射干扰。

◎多考虑电源和地线产生的噪音干扰,加去耦电容,加宽电源和地线,线宽符合地线>电源线>信号线规则,并采用大面积铜层做地线。

◎考虑信号串扰,远离地线,移开串扰信号或屏蔽被干扰的信号。

◎尽量保证地层的完整性。

从布局上考虑:

◎晶振尽量焊在PCB上,少用插座方式。

◎高频信号线尽可能远离敏感的模拟电路器件。

◎数字地与模拟地有一点短接或通过外界接口相连(如插座)。

◎SMT封装的晶振要尽量布局在系统PCB的B面,保证晶振只过一次回流焊。